Serial Peripheral Interface  Il Serial Peripheral Interface o SPI (pronuncia: esse pi i o spi), in informatica, indica un sistema di comunicazione seriale tra un microcontrollore e altri circuiti integrati o tra più microcontrollori. DescrizioneÈ un bus standard di comunicazione ideato dalla Motorola e sviluppato, in una sua variante, anche dalla National Semiconductor con il nome di bus MicrowireTM. La trasmissione avviene tra un dispositivo detto master e uno o più slave (letteralmente dall'inglese padrone e schiavo). Il master controlla il bus, emette il segnale di clock, decide quando iniziare e terminare la comunicazione[1]. Per quanto riguarda la velocità di scambio dei dati, in pratica la frequenza del clock, non vi è un limite minimo in quanto i dispositivi sono statici e possono mantenere se alimentati uno stato logico per un tempo indefinito. Comunque c'è un limite massimo che va determinato dai datasheet dei singoli dispositivi connessi e dal loro numero in quanto ogni dispositivo collegato al bus introduce sulle linee di comunicazione una capacità parassita. Il sistema di comunicazione di solito serve per lo scambio di dati tra dispositivi montati "sulla stessa scheda elettronica", o comunque tra schede elettroniche vicine tra di loro, in quanto non prevede particolari accorgimenti hardware per trasferire informazioni tra dispositivi lontani connessi con cavi soggetti a disturbi. Il sistema è comunemente definito a quattro fili, con questo si intende che le linee di connessione che portano i segnali sono in genere quattro. In ogni caso c'è una connessione di riferimento (0 Vdc comunemente e impropriamente indicata con GND) e quindi i fili fisicamente sono cinque. Discorso analogo si può fare su altri bus seriali definiti a due fili (I²C) o a un filo in quanto si considerano solo le linee di segnale e si sottintende la connessione di riferimento. TipiIl bus SPI si definisce:

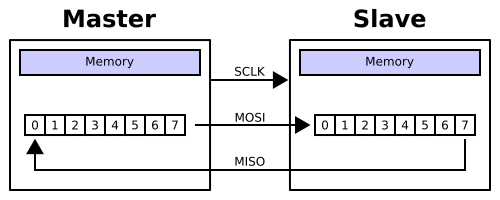

I segnaliEsso si basa su 4 segnali. Si riportano i nomi dei segnali che possono variare a seconda del costruttore. Consultare il datasheet del componente che si intende utilizzare in caso di dubbi:

Di questi il Chip Select (CS o SS) non è indispensabile in tutte le applicazioni. È facile confondersi nei nomi, spesso ambigui, sui segnali di trasferimento dei dati (ingressi e uscite). In ogni caso la consultazione dei datasheet dei dispositivi scelti dovrebbe chiarire ogni dubbio. Le denominazioni MOSI (Master Output Slave Input), MISO (Master Input Slave Output) sembrano essere quelle che comportano meno equivoci. Il segnale SCLK è il clock seriale che scandisce gli istanti di emissione e di lettura dei bit sulle linee di dati. È un segnale emesso dal master ed è quindi quest'ultimo a richiedere di volta in volta la trasmissione di una "parola"[2]. Il segnale SDI/MISO è la linea attraverso cui il dispositivo (master o slave) riceve il dato seriale emesso dalla controparte. Sullo stesso fronte di commutazione del clock, il dispositivo emette, con la stessa cadenza, il suo output ponendo il dato sulla linea SDO/MOSI (linea di output di dato). Nei dispositivi slave controllati singolarmente Vantaggi: comunicazione più rapida tra master e singoli slave. Nei dispositivi slave connessi a catena (daisy chain) Vantaggi: uso di un unico pin per selezionare i dispositivi. La comunicazioneLa trasmissione dei dati sul bus SPI si basa sul funzionamento dei registri a scorrimento (shift register). Ogni dispositivo, master o slave, è dotato di un registro a scorrimento interno i cui bit vengono emessi e contemporaneamente immessi, rispettivamente tramite l'uscita SDO/MOSI e l'ingresso SDI/MISO. Il registro può avere dimensione arbitraria, ma uguale per i dispositivi master e slave, e usualmente ha la dimensione di 8 bit. Il registro a scorrimento è un'interfaccia completa mediante cui vengono impartiti comandi e trasmessi dati che arrivano in modo seriale e che internamente sono prelevati, a fine trasmissione, in modo parallelo. A ogni impulso di clock i dispositivi che stanno comunicando sulle linee del bus emettono un bit dal loro registro interno rimpiazzandolo con un bit emesso dall'altro interlocutore. La sincronizzazione è fatta sui fronti di clock di salita o di discesa regolata da 2 parametri impostabili: CPOL e CPHA. CPOL regola la polarità del clock ovvero discrimina lo stato normale di riposo cui si porta la linea di clock quando non è attiva. Quando CPOL è impostato a 0, il clock, nel suo stato di riposo, si porta a livello logico basso; viceversa il clock si porta a livello logico alto durante il tempo di inattività se CPOL è impostato a 1. CPHA regola la fase del clock, ovvero il fronte di clock in cui il ricevente campiona il segnale in ingresso. Se CPOL=0 allora con CPHA possiamo scegliere di campionare il dato sul fronte di salita del segnale di clock, impostando CPHA=0, oppure sul fronte di discesa, impostando CPHA a 1. L'inverso accade se CPOL è settato a 1.  Generalmente queste opzioni sono impostabili sul dispositivo master e permettono di adattarlo a tutte le possibili varianti di dispositivi slave che normalmente vengono progettati per avere uno dei 4 modi di comunicazione possibili (tutte le combinazioni di CPOL e CPHA). Le modalità di funzionamento più spesso utilizzate dai dispositivi in commercio sono quelle con CPHA=CPOL=0 e con CPHA=CPOL=1. Il dato di output è emesso sempre in corrispondenza della prima transizione del clock. La comunicazione viene intrapresa sempre su iniziativa del dispositivo master che abilita lo slave tramite CS e successivamente impone il clock sulla linea dedicata. Con questa procedura ha inizio lo scambio dei bit tra i due registri. Alla fine di ogni parola trasmessa il contenuto del registro dello slave sarà passato al master e viceversa. Con opportune parole identificative si possono inviare comandi al dispositivo ricevente che potrà effettuare l'elaborazione assegnata ponendo quindi nel suo shift-register il dato richiesto che al prossimo ciclo di trasmissione verrà trasmesso al richiedente. Molti microcontrollori dispongono di un hardware dedicato per la gestione dell'SPI programmabile nei dettagli. Questo non è strettamente necessario per poter comunicare con un dispositivo slave SPI, come ad esempio una memoria EEPROM: in ogni caso si potrà implementare nel firmware delle funzioni dedicate al colloquio, che forse risulteranno più lente e occuperanno più spazio nel firmware di quelle disponibili con un blocco hardware dedicato, ma che comunque permetteranno di comunicare in modo efficiente con la periferica SPI poiché nella temporizzazione dei dati non c'è un limite di tempo massimo da rispettare. Infatti si tratta di dispositivi statici, che possono cioè sospendere a tempo indeterminato la comunicazione senza per questo avere perdita di dati: solo la loro velocità massima di trasmissione è limitata e possono funzionare anche a velocità molto bassa rispetto alla massima. Note

Voci correlate

Altri bus seriali

Altri progetti

Collegamenti esterni

|

Portal di Ensiklopedia Dunia