Sandy Bridgeマイクロアーキテクチャ(サンディブリッジ マイクロアーキテクチャ)とは、インテルによって開発されたマイクロプロセッサのマイクロアーキテクチャである。2011年1月6日に正式発表され[1]、第2世代Intel Coreプロセッサとして製品化された。第2世代Intel Coreプロセッサという言葉は、IntelがSandy Bridgeマイクロアーキテクチャで初めて用いた言葉であり、CoreマイクロアーキテクチャとNehalemマイクロアーキテクチャのCoreブランドのプロセッサは、前世代Intel Coreプロセッサと定義している。このことから、AVX命令セットの追加が第2世代Intel Coreプロセッサの定義だと推定される。特にCore ixプロセッサの世代を区別する場合は、Sandy Bridgeマイクロアーキテクチャを第2世代Intel Core ixプロセッサ、Nehalemマイクロアーキテクチャを前世代Intel Core ixプロセッサと区別している。

概要

イスラエルのハイファを拠点とする開発チームが開発を担当している。2007年のIDFでは、「Gesher」(ヘブライ語で橋を意味する)という名前で触れられたが、諸事情により現在の名前に変更された。2009年秋のIDFで2GHzで動作する試作品が公開された。ソケットは、サーバおよびハイエンド向けにLGA2011、普及帯にLGA1155がある[2]。32nmプロセスルールにて製造される。ラスベガスで開催されるCES2011にて米国時間2011年1月5日に発表され[1][3]、1月9日に発売解禁となった。しかし、2011年1月下旬に対応チップセットのシリアルATA周りに設計上の不具合が発見されたため、対応マザーボードの出荷が一時停止となり、修正版マザーボードの顧客向け出荷を2011年2月下旬に、量産を2011年4月から再開する見通しとなった。

特徴

- 新SIMD拡張命令セットIntel AVX

- 従来のSSEでは128bit幅だったSIMDレジスタが、256ビット幅に拡張される。FPUも同時に拡張され、1クロックで256ビットの演算が可能となる。これにより並列化のしやすい処理で最大2倍のパフォーマンスを発揮する。

- GPUの改良とネイティブな統合

- Clarkdaleとの比較で、GPU部は32nmプロセスで製造され、最高ターボ時1350MHzと高クロックであり、各種改良が加えられている。また、オンダイに統合され、L3キャッシュ(Last Levelキャッシュ)に接続している。

- 動画のハードウェアエンコード(Intel Quick Sync Video)を行うメディアエンジンを統合。

- PCIeコントローラーとDMIコントローラーのネイティブ統合。

- フロントエンド及び実行ユニットの改良

- 新しくデコード済み命令キャッシュを搭載、これによる実効命令フェッチ帯域の拡大と、分岐予測ミスペナルティの軽減。

- 分岐予測ユニットの実装強化、効率化。

- マクロフュージョンの追加サポート (CMP、TEST、ADD、SUB、AND、INC、DEC)。

- ダイナミック・エグゼキューション範囲の拡大。

- 多倍長演算の効率的な実装をサポートする拡張命令(w:Intel ADXを参照。ただし「ADX」および英語版にある「Multi-Precision Add-Carry Instruction Extensions」という表現のどちらも、インテルの公式資料等には見られないようである)

- 一般的な実行ストール(読み出しポート、ライトバック競合、バイパス・レイテンシー、パーシャル・ストール)の削減。

- XSAVE/XRSTORE 命令のパフォーマンスの向上、および新しいXSAVEOPT 命令の追加。

- 物理レジスタファイルの採用により、ユニット間のデータ移動&コピーを不要とし電力効率を改善。

- メモリ操作の改善

- メモリロードポートが2つに拡張され、ロード帯域幅が256ビットに倍増。

- バッファ増加によって、より多くのインフライトのロードおよびストアを同時に実行する。

- データプリフェッチの改善。

- コア間のインターコネクトをL3キャッシュ内に設けたリングバスとし、コア間の帯域幅の確保、電力効率の改善とともにコア数の増加に柔軟に対応する。

- 第2世代インテル ターボ・ブースト・テクノロジー

- CPUだけでなくGPUを含めた全てのコアに対してもターボ・ブーストが有効になり、発熱に余裕があればTDP枠を超え、よりダイナミックにクロックが上昇する。

Sandy Bridgeマイクロアーキテクチャは、4μOPs/クロックのデコード・リタイア、6つの命令発行ポートという命令レベルの並列度はNehalemマイクロアーキテクチャから変化していない。しかしながら、アウト・オブ・オーダー実行の機構が完全に再設計されている。

Pentium Proに端を発するP6マイクロアーキテクチャは、Nehalemに至るまでリオーダ・バッファとリザベーション・ステーションを用いたTomasuloのアルゴリズムに近い方式でアウト・オブ・オーダー実行を行っていた。この方式ではデータがレジスタファイル、リオーダ・バッファ、リザベーション・ステーションの3ヶ所に保持されるため、命令のデコード後(RFとROBからRS)、実行後(演算器からROBとRS)、リタイア時(ROBからRF)といったタイミングで逐一必要な場所へのデータの移動が発生する。一方Sandy Bridgeマイクロアーキテクチャでは、データの格納場所が物理レジスタファイルに一元化され、リオーダ・バッファとリザベーション・ステーションはレジスタファイルへの参照のみを保持し、データは保持しない (データを保持しないリザベーション・ステーションは、単にスケジューラと呼ばれるのが普通である)。このため、データの移動に伴うエネルギー消費が削減され、プロセッサの消費電力の低減に貢献している。

この物理レジスタファイルによるアウト・オブ・オーダー実行とデコード済み命令キャッシュの搭載は、Pentium 4のNetBurstマイクロアーキテクチャで既に行われたものである。これらはCoreマイクロアーキテクチャには反映されなかったが、Sandy Bridgeマイクロアーキテクチャで同時に復活したことになる。

製品一覧

プロセッサー・ナンバーの末尾にアルファベットが付いている製品があり、それぞれの意味は、

- K:オーバークロックができるようにTurbo Boost動作時の倍率のロックが解除されている。なお、ビジネス向け機能のTXT(英語版)、vPro、SIPPや仮想化技術のVT-dに非対応。

- S:省電力モデル。

- T:超省電力モデルで、このモデル向けにMini-ITX規格対応のマザーボードもリリースされる見込み[4]。

- M:モバイル向けデュアルコアモデルで、数字の末尾が0は通常電圧版、9は低電圧版、7は超低電圧版。

- XM・QM:モバイル向けクアッドコアモデルで、XMは内部倍率のロックが解除されている。

デスクトップ向け

- Sandy Bridge-E

Sandy Bridge-E

| ブランド

|

型番

|

CPU

|

TDP

(W)

|

対応メモリ

|

コア数

(スレッド数)

|

クロック (GHz)

|

キャッシュ (MB)

|

| 定格

|

ターボ

|

L2

|

L3

|

Core i7

Extreme

|

3970X

|

6 (12)

|

3.5 |

4.0

|

1.5

|

15

|

150

|

DDR3-1600

|

| 3960X

|

3.3 |

3.9

|

130

|

| Core i7

|

3930K

|

3.2

|

3.8

|

12

|

| 3820

|

4 (8)

|

3.6

|

1

|

10

|

- Sandy Bridge-DT

サーバー向け

- Sandy Bridge-EP

- Sandy Bridge-EN

- Sandy Bridge-DT

モバイル向け

- Sandy Bridge

組み込み向け

- Gladden

- Sandy Bridge

後継

後継は22nmにシュリンクされたIvy Bridgeマイクロアーキテクチャ。

脚注

関連項目

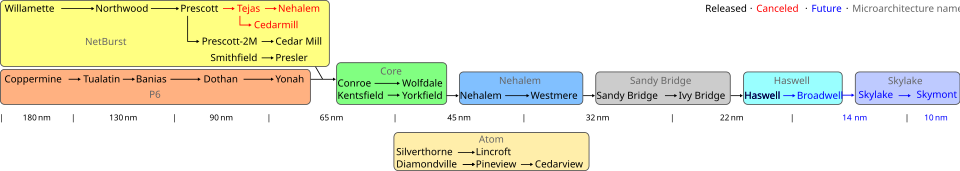

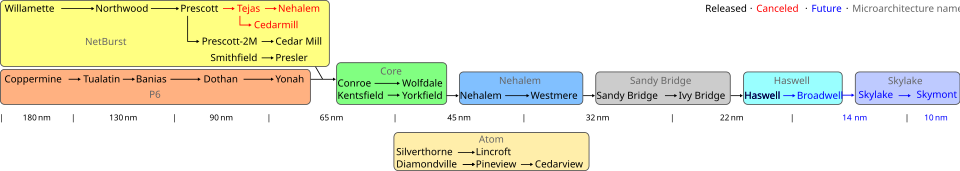

|

|---|

| 生産終了 |

|

|---|

| 現行 |

|

|---|

| その他 | |

|---|

マイクロ

アーキテクチャ |

| P5 |

P5ベースのコア |

|---|

| 0.90 μm | |

|---|

| 0.60 μm | |

|---|

| 0.35 μm | |

|---|

| 0.25 μm | |

|---|

|

|---|

| P6 |

P6ベースのコア |

|---|

| 0.50 μm | |

|---|

| 0.35 μm | |

|---|

| 0.25 μm | |

|---|

| 180 nm | |

|---|

| 130 nm | |

|---|

| 90 nm | |

|---|

| 65 nm | |

|---|

|

|---|

| NetBurst |

NetBurstベースのコア |

|---|

| 180 nm | |

|---|

| 130 nm | |

|---|

| 90 nm | |

|---|

| 65 nm | |

|---|

|

|---|

| Core |

|

|---|

| Atom |

Atomのマイクロアーキテクチャ |

|---|

| 参考 | |

|---|

| 45 nm | |

|---|

| 32 nm | |

|---|

| 22 nm | |

|---|

| 14 nm | |

|---|

| 10 nm | |

|---|

| Intel 7 | |

|---|

|

|---|

| Nehalem |

|

|---|

| Sandy Bridge |

Sandy Bridgeベースのコア |

|---|

| 32 nm | |

|---|

| 22 nm | |

|---|

|

|---|

| Haswell |

|

|---|

| Skylake |

|

|---|

| Cypress Cove |

|

|---|

| Sunny Cove |

|

|---|

| Willow Cove |

|

|---|

| Golden Cove (+Gracemont) |

|

|---|

| Raptor Cove (+Gracemont) |

|

|---|

| Redwood Cove (+Crestmont) |

Redwood Coveベースのコア |

|---|

| Intel 4 | |

|---|

| Intel 3 | |

|---|

|

|---|

| Lion Cove (+Skymont) |

|

|---|

|

|---|

|

|