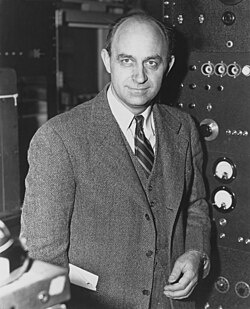

페르미 (마이크로아키텍처) 페르미(Fermi)는 엔비디아가 개발한 그래픽 처리 장치(GPU) 마이크로아키텍처의 코드네임으로, 테슬라 마이크로아키텍처의 후속으로 2010년 4월에 소매점에 처음 출시되었다. 이 아키텍처는 주로 지포스 400 시리즈와 500 시리즈에 사용되었다. 데스크톱 페르미 GPU는 모두 40nm 공정으로 제조되었으며, 모바일 페르미 GPU는 40nm 및 28nm 공정으로 제조되었다. 페르미는 마이크로소프트의 렌더링 API Direct3D 12 feature_level 11을 지원하는 엔비디아의 가장 오래된 마이크로아키텍처이다. 페르미는 케플러에 의해 계승되었으며, 지포스 600 시리즈, 지포스 700 시리즈, 지포스 800 시리즈에서는 케플러와 함께 사용되었는데, 후자 두 시리즈에서는 모바일 GPU에만 사용되었다. 워크스테이션 시장에서 페르미는 쿼드로 x000 시리즈, 쿼드로 NVS 모델, 엔비디아 테슬라 컴퓨팅 모듈에 사용되었다. 이 아키텍처는 이탈리아의 물리학자인 엔리코 페르미의 이름을 따서 명명되었다. 개요  그림의 관례: 주황색 - 스케줄링 및 디스패치; 녹색 - 실행; 하늘색 - 레지스터 및 캐시. 페르미 그래픽 처리 장치(GPU)는 30억 개의 트랜지스터를 특징으로 하며, 그 구성은 그림 1에 스케치되어 있다.

스트리밍 멀티프로세서각 SM은 32개의 단정밀 CUDA 코어, 16개의 로드/스토어 유닛, 4개의 특수 기능 유닛(SFU), 고속 온칩 메모리 64 KB 블록(L1+공유 메모리 하위 섹션 참조), L2 캐시 인터페이스(L2 캐시 하위 섹션 참조)를 특징으로 한다. 로드/스토어 유닛클럭당 16개의 스레드에 대한 소스 및 대상 주소를 계산할 수 있다. 캐시 또는 DRAM에서 데이터를 로드 및 저장한다. 특수 기능 유닛 (SFU)sin, cosine, reciprocal, square root와 같은 초월 함수 명령을 실행한다. 각 SFU는 클럭당 스레드별로 하나의 명령을 실행하며, 워프는 8클럭에 걸쳐 실행된다. SFU 파이프라인은 디스패치 유닛과 분리되어 있어 SFU가 사용 중인 동안 디스패치 유닛이 다른 실행 유닛으로 명령을 발행할 수 있다. CUDA 코어정수 산술 논리 장치 (ALU)표준 프로그래밍 언어 요구 사항과 일치하는 모든 명령에 대해 완벽한 32비트 정밀도를 지원한다.[{{{설명}}}] 또한 워크스테이션 및 서버 모델에서 64비트를 효율적으로 지원하도록 최적화되었지만, 소비자 버전에서는 인위적으로 기능이 제한되었다. 부동 소수점 장치 (FPU)새로운 IEEE 754-2008 부동 소수점 표준을 구현하여 단정밀도 및 배정밀도 연산을 위한 fused multiply-add (FMA) 명령을 제공한다. 클럭당 SM당 최대 16개의 배정밀도 fused multiply-add 연산을 수행할 수 있다.[1] Fused multiply-addFused multiply-add (FMA)는 곱셈과 덧셈(즉, A*B+C)을 최종 반올림 단계 한 번으로 수행하여 덧셈의 정밀도 손실을 방지한다. FMA는 연산을 개별적으로 수행하는 것보다 더 정확하다. 워프 스케줄링페르미 아키텍처는 두 단계의 분산 스레드 스케줄러를 사용한다. 각 SM은 구성도 그림 1에 표시된 네 개의 녹색 실행 열 중 두 개를 사용하는 명령을 발행할 수 있다. 예를 들어, SM은 첫 번째 열의 16개 코어의 16개 연산과 두 번째 열의 16개 코어의 16개 연산을 혼합하거나, 로드/스토어 유닛의 16개 연산과 SFU의 4개 연산을 혼합하거나, 프로그램에서 지정한 다른 조합을 혼합할 수 있다. 64비트 부동 소수점 연산은 처음 두 실행 열을 모두 필요로 하므로 32비트 연산 속도의 절반으로 실행된다. 듀얼 워프 스케줄러SM 수준에서 각 워프 스케줄러는 32개 스레드의 워프를 해당 실행 유닛에 분배한다. 각 SM은 두 개의 워프 스케줄러와 두 개의 명령 디스패치 유닛을 특징으로 하며, 두 개의 워프가 동시에 발행되고 실행될 수 있다. 듀얼 워프 스케줄러는 두 개의 워프를 선택하고, 각 워프에서 하나의 명령을 16개의 코어 그룹, 16개의 로드/스토어 유닛 또는 4개의 SFU에 발행한다. 대부분의 명령은 듀얼 발행이 가능하다. 두 개의 정수 명령, 두 개의 부동 명령, 또는 정수, 부동 소수점, 로드, 스토어 및 SFU 명령의 혼합이 동시에 발행될 수 있다. 배정밀도 명령은 다른 연산과 듀얼 디스패치를 지원하지 않는다. 성능페르미 GPU의 이론적 단정밀도 처리 능력(GFLOPS)은 2 (CUDA 코어당 FMA 명령당 사이클당 연산) × CUDA 코어 수 × 셰이더 클럭 속도(GHz)로 계산된다. 이전 세대 테슬라는 CUDA 코어와 SFU에 MAD+MUL을 병렬로 듀얼 발행할 수 있었지만, 페르미는 SM당 사이클당 32개 명령만 발행할 수 있어 32개의 CUDA 코어만 완전히 활용하게 되어 이 기능을 잃었다.[2] 따라서 SFU를 활용하여 CUDA 코어당 사이클당 2개 이상의 연산을 달성하는 것은 불가능하다. 페르미 GPU의 이론적 배정밀도 처리 능력은 GF100/110에서 단정밀도 성능의 절반이다. 그러나 실제로 이 배정밀도 능력은 전문가용 쿼드로 및 테슬라 카드에서만 사용할 수 있으며, 소비자용 지포스 카드는 1/8로 제한된다.[3] 메모리SM당 L1 캐시와 모든 연산(로드, 스토어 및 텍스처)을 처리하는 통합 L2 캐시. 레지스터각 SM은 32비트 레지스터 32K를 가진다. 각 스레드는 다른 스레드의 레지스터가 아닌 자신의 레지스터에 접근할 수 있다. CUDA 커널이 사용할 수 있는 최대 레지스터 수는 63개이다. 사용 가능한 레지스터 수는 작업량(및 이에 따른 자원 요구 사항)이 스레드 수에 따라 증가함에 따라 63개에서 21개로 점진적으로 감소한다. 레지스터는 약 8,000 GB/s의 매우 높은 대역폭을 가진다. L1+공유 메모리개별 스레드의 데이터를 캐시하거나(레지스터 스필링/L1 캐시) 여러 스레드 간에 데이터를 공유하는 데 사용할 수 있는 온칩 메모리이다. 이 64 KB 메모리는 공유 메모리 48 KB와 L1 캐시 16 KB 또는 공유 메모리 16 KB와 L1 캐시 48 KB로 구성할 수 있다. 공유 메모리는 동일한 스레드 블록 내의 스레드가 협력하도록 하며, 온칩 데이터의 광범위한 재사용을 용이하게 하고, 오프칩 트래픽을 크게 줄인다. 공유 메모리는 동일한 스레드 블록의 스레드에 의해 접근할 수 있다. 낮은 지연 시간 접근(10-20 사이클)과 매우 높은 대역폭(1,600 GB/s)을 중간 정도의 데이터(계산 시리즈의 중간 결과, 행렬 연산의 한 행 또는 열 데이터, 비디오 라인 등)에 제공한다. 데이비드 패터슨은 이 공유 메모리가 로컬 스크래치패드의 아이디어를 사용한다고 말한다.[4] 로컬 메모리로컬 메모리는 "스필링된" 레지스터를 저장하는 데 사용되는 메모리 위치로 의도되었다. 레지스터 스필링은 스레드 블록이 SM에서 사용 가능한 것보다 더 많은 레지스터 저장 공간을 요구할 때 발생한다. 로컬 메모리는 일부 자동 변수(장치 코드에서 __device__, __shared__, or __constant__ 한정자 없이 선언된 변수)에만 사용된다. 일반적으로 자동 변수는 다음의 경우를 제외하고 레지스터에 상주한다. (1) 컴파일러가 상수 값으로 인덱싱되는 배열임을 확인할 수 없는 경우; (2) 너무 많은 레지스터 공간을 차지할 큰 구조체 또는 배열; 커널이 SM에서 사용 가능한 것보다 더 많은 레지스터를 사용할 때 컴파일러가 로컬 메모리로 스필링하기로 결정한 모든 변수. L2 캐시16개의 SM에서 공유되는 통합 768 KB L2 캐시는 CPU 호스트와의 복사를 포함하여 글로벌 메모리로의 모든 로드 및 스토어 연산과 텍스처 요청을 처리한다. L2 캐시 하위 시스템은 스레드 블록 또는 심지어 커널 간에 공유되어야 하는 데이터 접근을 관리하는 데 사용되는 원자적 연산도 구현한다. 글로벌 메모리글로벌 메모리(VRAM)는 모든 스레드가 직접 접근할 수 있으며 PCIe 버스를 통해 호스트 시스템도 접근할 수 있다. 400-800 사이클의 높은 지연 시간을 가진다. 비디오 압축/압축엔비디아 NVDEC(이전에는 NVCUVID라고 불림) 및 엔비디아 퓨어비디오를 참조하십시오. 엔비디아 NVENC 기술은 아직 사용할 수 없었지만, 후속 제품인 케플러에 도입되었다. 페르미 칩

같이 보기각주

일반

외부 링크

|

Portal di Ensiklopedia Dunia