Технологический процесс в электронной промышленности  Технологический процесс полупроводникового производства — технологический процесс по изготовлению полупроводниковых (п/п) изделий и материалов; часть производственного процесса по изготовлению п/п изделий (транзисторов, диодов и т. п.); состоит из: последовательности технологических (обработка, сборка) и контрольных операций. При производстве п/п изделий применяется фотолитография и литографическое оборудование. Разрешающая способность (в мкм и нм) этого оборудования (т. н. проектные нормы) и определяет название применяемого конкретного технологического процесса. Совершенствование технологии и пропорциональное уменьшение размеров п/п структур способствуют улучшению характеристик (размеры, энергопотребление, рабочие частоты, стоимость) полупроводниковых приборов (микросхем, процессоров, микроконтроллеров и т. д.). Особую значимость это имеет для процессорных ядер, в аспектах потребления электроэнергии и повышения производительности, поэтому ниже указаны процессоры (ядра) массового производства на данном техпроцессе. Этапы технологического процесса при производстве микросхемТехнологический процесс производства полупроводниковых приборов и интегральных микросхем (микропроцессоров, модулей памяти и др.) включает нижеследующие операции.

Технологии производства полупроводниковой продукции с субмикронными размерами элементов основаны на чрезвычайно широком круге сложных физико-химических процессов: получение тонких плёнок термическим и ионно-плазменным распылением в вакууме, механическая обработка пластин производится по 14-му классу чистоты с отклонением от плоскостности не более 1 мкм, широко применяется ультразвук и лазерное излучение, используются отжиг в кислороде и водороде, рабочие температуры при плавлении металлов достигают более 1500 °C, при этом диффузионные печи поддерживают температуру с точностью 0,5 °C, широко применяются опасные химические элементы и соединения (например, белый фосфор). Всё это обусловливает особые требования к производственной гигиене, так называемую «электронную гигиену», ведь в рабочей зоне обработки полупроводниковых пластин или на операциях сборки кристалла не должно быть более пяти пылинок размером 0,5 мкм в 1 л воздуха. Поэтому в чистых комнатах на фабриках по производству подобных изделий все работники обязаны носить специальные комбинезоны[1]. В рекламных материалах Intel спецодежда работников получила название bunny suit («костюм кролика»)[2][3].

Сверхвысокочистый природный кварц является одним из важнейших компонентов, используемых при производстве полупроводников — он применяется при изготовлении тиглей, необходимых для очистки кремниевых пластин[4]. В процессе производства используется множество токсичных материалов, к ним относятся:

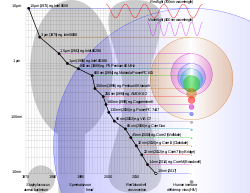

Техпроцессы 1970—1980-хРанние техпроцессы, до стандартизации NTRS (National Technology Roadmap for Semiconductors) и ITRS, обозначались «xx мкм» (xx микрон), где xx сперва обозначало техническое разрешение литографического оборудования, затем стало обозначать длину затвора транзистора, полушаг линий металла (half pitch) и ширину линий металла. В 1970-х существовало несколько техпроцессов, в частности 20, 10, 8, 6, 4, 3, 2 мкм; в среднем, каждые три года происходило уменьшение шага с коэффициентом 0,7[6] 3 мкм3 мкм — техпроцесс, соответствующий уровню технологии, достигнутому в 1975 году Zilog (Z80) и в 1979 году Intel (Intel 8086). Соответствует линейному разрешению литографического оборудования, примерно равному 3 мкм. 1,5 мкм1,5 мкм — техпроцесс, соответствующий уровню технологии, достигнутому Intel в 1982 году. Соответствует линейному разрешению литографического оборудования, примерно равному 1,5 мкм. 0,8 мкм0,8 мкм — техпроцесс, соответствующий уровню технологии, достигнутому в конце 1980-х — начале 1990-х годов компаниями Intel и IBM.

0,6 мкм / 0,5 мкмТехпроцесс, достигнутый производственными мощностями компаниями Intel и IBM в 1994—1995 годах.

Техпроцессы 1990-х годовОбозначения для техпроцессов, внедренных начиная с середины 1990-х годов, были стандартизованы NTRS и ITRS и стали называться «Technology Node» или «Cycle». Реальные размеры затворов транзисторов логических схем стали несколько меньше, чем обозначено в названии техпроцессов 350 нм — 45 нм благодаря внедрению технологий resist-pattern-thinning и resist ashing. С этих пор коммерческие названия техпроцессов перестали соответствовать длине затвора[6][7]. С переходом на следующий техпроцесс ITRS площадь, занимаемая стандартной ячейкой 1 бита памяти SRAM, в среднем уменьшалась вдвое. В период с 1995 по 2008 года такое удвоение плотности транзисторов происходило в среднем каждые 2 года[6]. 350 нм350 нм — техпроцесс, соответствующий уровню технологии, достигнутому в 1995—1997 годах ведущими компаниями — производителями микросхем, такими как Intel, IBM, и TSMC. Соответствует линейному разрешению литографического оборудования, примерно равному 0,35 мкм.

250 нм250 нм — техпроцесс, соответствующий уровню технологии, достигнутому в 1998 году ведущими компаниями — производителями микросхем. Соответствует линейному разрешению литографического оборудования, примерно равному 0,25 мкм. Используется до 6 слоёв металла, минимальное количество литографических масок — 22[источник не указан 3736 дней].

180 нм180 нм — техпроцесс, соответствующий уровню технологии, достигнутому в 1999 году ведущими компаниями — производителями микросхем. Соответствует удвоению плотности размещения по отношению к предыдущему техпроцессу 0,25 мкм. Также впервые используются внутренние соединения на основе медных соединений (Copper-based chips) с меньшим сопротивлением, чем у ранее применявшегося алюминия. Содержит до 6-7 слоёв металла. Минимальное количество литографических масок — около 22[источник не указан 3736 дней].

130 нм130 нм — техпроцесс, соответствующий уровню технологии, достигнутому в 2001 году ведущими компаниями — производителями микросхем. В соответствии с моделями ITRS[8], соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 0,18 мкм.

Техпроцессы менее 100 нмДля обозначения более тонких техпроцессов разные технологические альянсы могут следовать различным рекомендациям (Foundry/IDM). В частности, TSMC использует обозначения 40 нм, 28 нм и 20 нм для техпроцессов, сходных по плотности с процессами Intel 45 нм, 32 нм и 22 нм соответственно[9]. 90 нм90 нм — техпроцесс, соответствующий уровню полупроводниковой технологии, которая была достигнута к 2002—2003 годам. В соответствии с моделями ITRS[8], соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 0,13 мкм. Технологический процесс с проектной нормой 90 нм часто используется с технологиями напряженного кремния, а также c новыми диэлектрическими материалами с низкой диэлектрической проницаемостью (low-k-диэлектрик).

65 нм65 нм — техпроцесс, соответствующий уровню технологии, достигнутому к 2004 году ведущими компаниями — производителями микросхем. В соответствии с моделями ITRS[8], соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 90 нм.

45 нм / 40 нм45 нм и 40 нм — техпроцесс, соответствующий уровню технологии, достигнутому к 2006—2007 годам ведущими компаниями — производителями микросхем. В соответствии с моделями ITRS[8], соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 65 нм. Для микроэлектронной промышленности стал революционным, так как это был первый техпроцесс, использующий технологию high-k/metal gate[12][13] (HfSiON/TaN в технологии компании Intel), для замены физически себя исчерпавших SiO2/poly-Si

32 нм / 28 нм32 нм — техпроцесс, соответствующий уровню технологии, достигнутому к 2009—2010 годам ведущими компаниями — производителями микросхем. В соответствии с моделями ITRS[8], соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 45 нм. Осенью 2009 компания Intel находилась на этапе перехода к этому новому техпроцессу[14][15][16][17][18]. С начала 2011 начали производиться процессоры по данному техпроцессу. В третьем квартале 2010 года на новых мощностях расположенной на Тайване фабрики Fab 12 компании TSMC начался серийный выпуск продукции по технологии, получившей маркетинговое обозначение «28-нанометров»[19] (не является обозначением, рекомендуемым ITRS).

В мае 2011 по технологии 28 нм фирмой Altera была выпущена самая большая в мире микросхема, состоящая из 3,9 млрд транзисторов[24]. 22 нм / 20 нм22 нм — техпроцесс, соответствующий уровню технологии, достигнутому к 2009—2012 годам ведущими производителями микросхем. Соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 32 нм. 22-нм элементы формируются путём фотолитографии, в которой маска экспонируется светом с длиной волны 193 нм[25][26]. В 2008 году на ежегодной выставке высоких технологий International Electron Devices Meeting в Сан-Франциско технологический альянс компаний IBM, AMD и Toshiba продемонстрировал ячейку памяти SRAM, выполненную по 22-нм техпроцессу из транзисторов типа FinFET, которые, в свою очередь, выполняются по прогрессивной технологии high-k/metal gate (затворы транзистора изготавливаются не из кремния, а из гафния), площадью всего 0,128 мкм² (0,58×0,22 мкм)[27]. Также о разработке ячейки памяти типа SRAM площадью 0,1 мкм², созданной по техпроцессу 22 нм, объявили IBM и AMD[28]. По такой технологии производятся (с начала 2012 года):

16 нм / 14 нм

По состоянию на май 2014 компания Samsung продолжала разработки техпроцессов 14 нм LPE/LPP[30]; а выпускать процессоры для Apple планирует в 2015 году[31]. По состоянию на сентябрь 2014 TSMC продолжала разработку 16-нм техпроцесса на транзисторах с вертикально расположенным затвором (Fin Field Effect Transistor, FinFET) и планировала начать 16-нм производство в 1 квартале 2015 года[32]. Согласно экстенсивной стратегии фирмы Intel, уменьшение техпроцесса до 14 нм изначально ожидалось через год после представления чипа Haswell (2013); процессоры на новом техпроцессе будут использовать архитектуру с названием Broadwell. Для критических слоёв техпроцесса 14 нм Intel потребовалось применение масок с технологией Inverse Lithography (ILT) и SMO (Source Mask Optimization)[33].

Компания МЦСТ в 2021 году представила 16-нм процессор Эльбрус-16С. В апреле 2018 года AMD представила процессоры Zen+ на улучшенном 14-нм техпроцессе, условно обозначенном как «12 нм»:

Техпроцессы с 2010-х годов по настоящее время12 нм / 10 нмТайваньский производитель United Microelectronics Corporation (UMC) сообщил, что присоединится к технологическому альянсу IBM для участия в разработке 10-нм CMOS-техпроцесса[35]. В 2011 году публиковалась информация о планах Intel по внедрению 10-нм техпроцесса к 2018 году[36], в октябре 2017 Intel сообщил о планах начать производство до конца 2017 года[37], но в итоге, после выпуска крайне ограниченной партией 10-нм мобильного процессора Intel Core i3-8121U в 2018, массовое производство процессоров Intel по 10-нм техпроцессу началось только в 2019 году для мобильных устройств и в 2020 для десктопных. Пробный выпуск продукции по нормам 10 нм намечался компанией TSMC на 2015 год, а серийный — на 2016[38]. В начале 2017 года выпуск 10 нм составлял около 1 % от продукции TSMC[39]. Samsung запустил 10-нм производство в 2017 году[40].

7 нм В 2018 году на фабриках TSMC началось производство мобильных процессоров Apple A12[43], Kirin 980[44], а также Snapdragon 855[45]. Производство 7-нм процессоров на архитектуре x86 задерживается, первые образцы на данной архитектуре появляются не раньше 2019 года. Согласно интернет-изданию Russian Tom’s Hardware Guide, с помощью первого поколения 7-нм техпроцесса TSMC может разместить 66 миллионов транзисторов на квадратном миллиметре, в то же время с помощью 10-нм техпроцесса Intel может разместить на аналогичной площади 100 миллионов транзисторов[46]. Переход на второе поколение[прояснить] 7-нм техпроцесса у TSMC состоялся в 2019 году. Первым массовым продуктом, произведённым по этому техпроцессу, стал Apple A13. Intel при 7-нм техпроцессе (ожидается в 2022 году)[47], согласно изданию Hardwareluxx, планирует разместить 242 млн транзисторов на квадратном миллиметре[48]. Китайская SMIC с 2021 года выпускает 7-нм чипы на своём старом оборудовании[49] Продукты:

6 нм / 5 нм16 апреля 2019 года компания TSMC анонсировала освоение технологического процесса 6 нм в рисковом производстве, что позволяет повысить плотность упаковки элементов микросхем на 18 %, данный техпроцесс является более дешёвой альтернативной техпроцессу 5 нм, он позволяет легко масштабировать топологии, разработанные для 7 нм[53]. В первой половине 2019 года TSMC начала рисковое производство чипов по 5-нм техпроцессу[54]; переход на эту технологию позволяет повысить плотность упаковки электронных компонентов на 80 % и повысить быстродействие на 15 %[55]. Согласно China Renaissance, техпроцесс TSMC N5 включает в себя 170 миллионов транзисторов на квадратный миллиметр[56]. Samsung в марте 2017 года презентовал дорожную карту по выпуску процессоров по 7- и 5-нм технологиям. В ходе презентации вице-президент Samsung по технологии Хо-Кью Кан отметил, что многие производители столкнулись с проблемой при разработке технологий меньше 10 нм. Однако Samsung справилась с задачей, ключом к которой стало использование полевого транзистора с «кольцевым» затвором (GAAFET[англ.]*). Эти транзисторы позволят компании продолжить уменьшать элементы до размера 7 и 5 нм. Для изготовления пластин компания применит технологию экстремальной ультрафиолетовой литографии (EUV)[57]. В 2020 году Samsung начал массовое производство 5-нм чипов[58]. Плотность техпроцесса Samsung 5LPE при этом составила 125—130 миллионов транзисторов на квадратный миллиметр[56]. Первым массовым продуктом, произведённым по 5-нм техпроцессу, стал Apple A14, представленный в сентябре 2020 года. В ноябре 2020 года был представлен процессор Apple M1, предназначенный для компьютеров линейки Macintosh. 4 нмВ конце 2021 г. состоялся анонс первого в мире 4-нанометрового процессора. Над ним работала компания MediaTek, и он был предназначен для смартфонов. Его производством занималась тайваньская TSMC. Массовое производство было запущено в 4 квартале 2021 года. Первые смартфоны на его основе появились в I квартале 2022 г[59][60]. В конце 2021 года TSMC также начала производство чипов по техпроцессу N4 (4-нм). Эта технология была призвана обеспечить дополнительные преимущества по производительности и энергопотреблению по сравнению с N5, но с теми же принципами и инфраструктурой проектирования и программами моделирования SPICE. Кроме того, N4 расширила возможности использования инструментов литографии в крайнем ультрафиолетовом диапазоне (EUV), что сократило количество маскирующих слоёв, этапов производства, а следовательно, рисков и затрат. На полную мощность производство вышло в 2022 году[61]. В сентябре 2022 года был представлен мобильный процессор Apple A16, выпущенный по 4 нанометрам. Samsung начала массовое производство 4-нм чипов третьего поколения в первой половине 2023 года[62]. 3 нмИсследовательский центр ИМЕК (Бельгия) и компания Cadence Design Systems создали технологию и в начале 2018 года выпустили первые пробные образцы микропроцессоров по технологии 3 нм[63]. По данным TSMC, у которой 3-нанометровая топология появилась в конце 2020 году, переход на неё позволит нарастить производительность процессоров на 10—15 % в сравнении с нынешними 5-нм чипами, а их энергопотребление снизится на 25—30 %[64]. Ожидается, что пластина с 3-нм чипами будет стоить на 25 % больше, чем пластина 5-нм чипов[65]. 30 июня 2022 года Samsung заявила, что начала массовое производство 3-нм процессоров, став первой компанией, достигшей этого[66][67], но речь идет о технологии первого поколения, которая применяется для выпуска относительно простых решений для ускорения майнинга. Структурно более сложные компоненты Samsung рассчитывает выпускать уже с использованием 3-нм технологии второго поколения, которая будет освоена к 2024 году (при этом, Samsung рассчитывает превзойти конкурентов типа TSMC и Intel, перейдя на использование технологии GAAFET)[68]. В начале мая 2024 года Samsung представила свой первый мобильный процессор, разработанный с использованием передового 3-нм техпроцесса с транзисторами GAAFET (Gate-All-Around Field-Effect Transistor), при этом почти весь дизайн и оптимизация были выполнены при помощи инструментов электронно-компьютерного проектирования (EDA) на базе искусственного интеллекта, созданных компанией Synopsys[69]. В начале июля 2024 года компания Samsung официально представила свой новый 3-нм процессор под названием Exynos W1000. Новый чип оснащен большим ядром Cortex-A78, работающим на частоте 1,6 ГГц, и четырьмя меньшими ядрами Cortex-A55, работающими на частоте 1,5 ГГц[70]. Intel в сотрудничестве с TSMC планировала в начале 2023 года выпустить свой первый 3-нанометровый процессор (у Intel есть проект дизайна как минимум двух 3-нанометровых чипов, один из них ориентирован на ноутбуки, а второй предназначен для использования в серверах). Также к переходу на 3-нм готовится и Apple с выходом новой модификации планшета iPad Pro[64]. 2 нмВ мае 2021 года IBM заявила о создании первого 2-нм чипа[71][72]. TSMC удалось успешно запустить тестовое производство 2-нм чипов. Тестовый выпуск стартовал летом 2024 года на заводе TSMC на севере Тайваня[73]. Согласно имеющимся данным, выход годной продукции с 2-нм техпроцессом уже превышает 60%, благодаря чему переход к массовому производству может увеличить квартальную выручку до $30 млрд во второй половине 2025 года. Пробное 2-нм производство оказалось настолько успешным, что компания перейдет к массовому выпуску 2-нм чипов уже ближе к концу 2025 года. Ожидается, что ежемесячный объём может достигнуть 80 тысяч пластин в конце 2025 года[74]. Уже в 2026 году TSMC ожидает достичь производственной мощности в 130 тысяч пластин ежемесячно[75]. Центральное место в 2-нм техпроцессе занимает технология транзисторов с круговым затвором (GAA, gate-all-around), которая приходит на смену FinFET, доминировавшей в индустрии на протяжении последнего десятилетия. GAA обеспечивает более полный контроль над потоком электронов в транзисторе, что позволяет существенно увеличить плотность размещения элементов на кристалле. Результатом становится прирост производительности до 15 % и снижение энергопотребления на внушительные 25-30 % по сравнению с предыдущими поколениями техпроцессов[76]. Ожидается, что первые коммерческие продукты на базе 2-нм технологии TSMC появятся уже в 2026 году. Apple планирует использовать новый техпроцесс для своего будущего чипа A20 в iPhone 18, а Qualcomm готовит как минимум два процессора, включая Snapdragon 8 Elite Gen 3[77]. Samsung ускоряет подготовку мощностей к запуску массового производства чипов по 2-нм техпроцессу. В конце 2024 года компания начала установку передового оборудования на заводе S3 в Хвасоне для создания производственной линии 2 нм. К первому кварталу 2025 года эта линия, как рассчитывает компания, сможет производить 7000 пластин согласно 2-нм техпроцессу в месяц[78]. В 2-нм технологическом процессе важную роль играет новая технология транзисторов с круговым затвором GAAFET. Во второй половине 2025 года, Samsung планирует запустить производство 2-нм пластин в больших объёмах, что обеспечит выполнение крупных заказов на них, а также увеличить свой портфель специализированных процессов. Компания попытается заполучить прибыльных клиентов, чтобы не отставать от TSMC, которая уже начала принимать заказы на пластины 2-нм[79]. По состоянию на апрель 2025 года показатель выхода годных чипов на этапе тестирования превысил 40%, что существенно лучше предыдущих результатов (20-30%) в 2024 году. Это позволит Samsung вовремя запустить выпуск флагманского мобильного чипа Exynos 2600[80]. Новейший чип Exynos 2600, построенный на 2-нм процессе Samsung SF2, может использоваться в линейке Galaxy S26[81]. Qualcomm, Apple, Nvidia и AMD планируют воспользоваться мощностями Samsung для производства своих чипов по нормам 2 нм, вместо того чтобы оставаться с TSMC[82][83]. Также компания строит современный завод по выпуску полупроводниковых чипов на 2-нм техпроцессе в Тейлоре (штат Техас)[84]. Компания Intel, изначально планировавшая использовать техпроцесс 20A для адаптации к новшествам в компоновке транзисторов и подводу питания с оборотной стороны кремниевой пластины, не делает серьёзных ставок на него в серийном производстве. Компания решила не выводить на рынок техпроцесс 20A для концентрации ресурсов на внедрении более совершенного 18A[85]. В декабре 2024 года японская компания Rapidus объявила о начале опытного производства чипов по 2-нм технологии. Rapidus станет первой японской фирмой, использующей оборудование EUV от ASML. Уже в апреле 2025 года компания сможет начать выпуск прототипов 2-нм чипов для своих клиентов на опытной линии, установленной на предприятии на острове Хоккайдо. К июню Rapidus сможет начать поставки образцов 2-нм чипов, которые были разработаны компанией Broadcom. Если первые итоги сотрудничества устроят эту компанию, то массовый выпуск 2-нм чипов для её нужд Rapidus освоит к 2027 году[86][87]. 3 марта 2025 года компания Marvell вместе с TSMC создала первый рабочий чип по техпроцессу 2 нм. Весной 2024-го обе компании сообщили, что взялись за такой проект. Marvell разработала чип для инфраструктуры ИИ и облачных вычислений — своей ключевой IP-сферы. Он войдет в платформу ускорителей (XPU)[88]. 1,8 нмРуководство Intel не раз утверждало, что не станет долго тянуть с предоставлением своим клиентам доступа к технологии Intel 18A после того, как освоит по ней выпуск продукции для собственных нужд. Теперь на своём сайте компания сообщает, что готова предоставить сторонним заказчикам цифровые проекты, созданные по технологии 18A, в первом полугодии 2025 года. По плотности размещения транзисторов техпроцесс Intel 18A готов поспорить с TSMC N2, по сравнению с предшественником Intel 3 он повышает производительность на ватт на 15 %, а плотность размещения транзисторов в этом сравнении на 30 % выше. Компания возлагает большие надежды на 18A-технологию, которая включает инновационные решения, такие как транзисторы RibbonFET и систему питания с обратной стороны чипа. Эти технологии позволяют повысить производительность, снизить энергопотребление и увеличить плотность транзисторов. Как подчеркнул Панкаж Марриа: «Это достижение — результат упорного труда всех участников процесса и инноваций»[89][90]. В начале апреля 2025 года Intel объявила о важном этапе в разработке своего передового техпроцесса Intel 18A. На конференции Intel Vision 2025 Кевин О'Бакли, старший вице-президент и глава Intel Foundry Services, сообщил, что 18A уже перешёл на этап пробного производства (risk production), при котором осваиваются первые производственные циклы для отладки технологии. Также Intel уже готовит тестовые чипы для внешних заказчиков, их производство начнётся в середине 2025 года, а массовый выпуск 18A стартует во второй половине 2025 года[91]. 29 апреля 2025 года на мероприятии Intel Foundry Direct компания представила Intel 18A-P — высокопроизводительную версию базового техпроцесса, уже запущенную в пробное производство. Intel 18A-P обеспечивает повышение производительности на ватт в пределах 5-10% относительно стандартного 18A. Но ещё больший интерес вызвала версия Intel 18A-PT, предназначенная для применения вместе с технологией Foveros Direct 3D, благодаря которой становится возможной трёхмерная упаковка кристаллов, когда чипы можно будет размещать друг над другом, увеличив тем самым производительность и плотность компоновки. Аналогичную технологию TSMC уже применяет в чипах AMD с 3D V-Cache[92]. Intel планирует использовать Foveros Direct 3D в своих будущих процессорах Clearwater Forest[93]. В будущем Intel начнет выпуск коммерческих чипов, которые будут использоваться в реальных продуктах. Первые CPU по техпроцессу Intel 18A должны выйти уже во втором полугодии 2025 года. Это будут мобильные чипы Panther Lake. Кроме того, 18A-технология будет использоваться для создания серверных процессоров Xeon 7 под кодовым названием Clearwater Forest. Эти процессоры, предназначены для использования в дата-центрах и обещают стать новым словом в энергоэффективности и производительности[94][95]. 1,6 нмВ конце апреля 2024 года TSMC представила свою новую технологию A16 на Североамериканском технологическом симпозиуме в Санта-Кларе, Калифорния. Представители TSMC пояснили, что 1,6-нм технология способна значительно увеличить плотность размещения логических элементов и их быстродействие по сравнению с техпроцессом N2P. В частности, скорость переключения транзисторов вырастет на 8-10 % при неизменном напряжении, энергопотребление удастся снизить на 15-20 % при том же быстродействии, а в серверном сегменте плотность размещения транзисторов удастся увеличить в 1,1 раза. Новая технология предусматривает использование нанолистовых транзисторов gate-all-around (GAAFET), которые состоят из тончайших слоёв кремния. Попутно сообщается, что помимо структуры транзисторов с окружающим затвором, которую конкурирующая Samsung начала использовать ещё в рамках своего 3-нм техпроцесса, компания TSMC при выпуске чипов по технологии A16 будет использовать и подвод питания с оборотной стороны кремниевой пластины (BSPDN) – Super Power Rail[95]. Это новый подход, когда питание подаётся с обратной стороны кремниевой пластины, что позволяет избежать сложной внутренней проводки и повысить энергоэффективность. Такая система улучшает плотность транзисторов и их питание, что критически важно для производительности. Реализация TSMC – одна из самых сложных, что, вероятно, стало причиной отказа от BSPDN в процессах N2P и N2X. Она разработана специально для ИИ и высокопроизводительных процессоров, которым требуется сложная сигнальная разводка и плотная сеть питания[96]. Компания решила отложить внедрение этой инновационной технологии для 2-нм техпроцесса, планируя использовать ее в поколении 1,6-нм чипов A16[76]. TSMC намерена начать производство 1,6-нанометровых процессоров во второй половине 2026 года. Компания отметила, что первыми новейшие чипы получат разработчики решений искусственного интеллекта, а не производители смартфонов, как это обычно бывает[97]. Новый коннектор, который используют для подключения чипа к источнику питания, новая сеть подачи энергии будет наиболее полезна в основном для процессоров искусственного интеллекта и высокопроизводительных вычислений, требующих сложной проводки и плотной сети энергоподачи[98]. По словам представителей TSMC, компания ускорила разработку технологии A16 с учётом потребностей неких компаний, интересующихся возможностью выпуска чипов для ИИ-систем с её помощью. Примечательно, что литографические сканеры с высоким значением числовой апертуры (High-NA EUV) для выпуска 1,6-нм продукции TSMC, скорее всего, не потребуются[90]. TSMC не сказала, какие именно компании первыми получат доступ к техпроцессу 1,6 нм. Эксперты полагают, что первыми клиентами для этих передовых решений станут компании Apple, NVIDIA и Qualcomm. Современные чипы, созданные с использованием этой технологий, обеспечат ещё большую производительность, энергоэффективность и плотность транзисторов, что особенно важно для рынков смартфонов, игровых консолей, ИИ и серверных решений[99]. Также TSMC приняла решение построить в Аризоне третий завод, на котором планируется выпуск чипов A16 по техпроцессу 1,6 нм к 2030 году. Первый завод уже выпускает 4-нм чипы, второй будет ориентирован на 3- и 2-нм техпроцессы, а третий — на перспективную технологию A16. Новый завод необходим для поддержки лидерства США в области искусственного интеллекта и расширения производственной базы компании на американской территории. Этот шаг станет частью масштабного расширения компании за пределами Тайваня[100]. 1,4 нмВ конце апреля 2025 года TSMC анонсировала 1,4-нм техпроцесс A14 на транзисторах Gate-All-Around (GAA) второго поколения, получивший кодовое название Angstrom. Технология обеспечит прирост производительности на 10–15 % при том же энергопотреблении, а также снижение потребляемой мощности на 25–30 % при сохранении частоты и логической сложности по сравнению с 2-нм N2. Плотность логических элементов повысится на 23 %, а общая плотность транзисторов в условиях смешанного проектирования — 20 %. Компания сообщила, что A14 — это новый техпроцесс, разработанный с нуля, так что для него не подойдут дизайны чипов, спроектированные для предыдущих техпроцессов. Новая технология построена на транзисторах с нанолистами (nanosheets) второго поколения, произведённых с использованием новейшей технологии GAA. Это отличает его от техпроцесса N2P, основанного на платформе N2, и от A16, представляющего собой улучшенный N2P с системой подачи питания с обратной стороны (Backside Power Delivery — BSPDN). Несмотря на отсутствие BSPDN, техпроцесс A14 сохраняет высокую эффективность благодаря использованию транзисторов с нанолистами второго поколения. Одним из ключевых компонентов технологии является NanoFlex Pro — усовершенствованная архитектура стандартных ячеек, предоставляющая разработчикам гибкость при конфигурировании логических блоков с учётом трёх важных метрик: производительности, энергопотребления и площади кристалла. Массовое производство запланировано на 2028 год, а версия с подачей питания с обратной стороны чипа дебютирует в 2029 году[101]. Поскольку у TSMC разнообразный список клиентов, процесс следующего поколения, как ожидается, будет использоваться в будущих продуктах таких технологических гигантов, как Nvidia, Apple, AMD и других[102]. Ожидается, что Apple станет первой компанией, которая получит доступ к этой технологии. IPhone 20 будет первым смартфоном с подобным процессором[103]. Компания Intel обнародовала свежие планы по освоению передовых техпроцессов. В том числе компания анонсировала 1,4-нм техпроцесс Intel 14A, который станет первой в мире технологией производства чипов с использованием литографии в сверхжёстком ультрафиолете с высокой числовой апертурой (High-NA EUV). Массовое производство намечено на 2027 год[104]. Глава компании Лип Бу Тан на мероприятии Intel Foundry Direct 2025 объявил о значительных успехах на направлении контрактного производства полупроводников. В частности, Intel привлекла первых клиентов для своего перспективного техпроцесса 14A, который станет следующим шагом после 18A. Уже несколько заказчиков готовятся к получению тестовых 1,4-нм чипов. Данный техпроцесс предложит транзисторы с нанолистами RibbonFET второго поколения. Также было отмечено, что Intel 14A будет использовать второе поколение технологии подачи питания с тыльной стороны кристалла PowerVia. Она будет представлять собой более совершенную и сложную схему, которая подает питание непосредственно на исток и сток каждого транзистора через специализированные контакты, что минимизирует сопротивление и максимизирует энергоэффективность. Это более прямое и эффективное подключение, чем нынешняя схема PowerVia от Intel, которая подключается к транзисторам на уровне контактов с помощью нано-транзисторов. Если всё пойдёт по плану, Intel опередит TSMC, которая планирует выпустить аналог в лице A14 только к 2028 году и без использования High-NA EUV[92]. Samsung ко второму кварталу 2025 года рассчитывает построить производственную линию для 1,4-нм техпроцесса на предприятии S5 на втором заводе в Пхёнтхэке (Pyeongtaek Plant 2). Она сможет производить 2000–3000 пластин ежемесячно. Производство начнётся в 2027 году[105][106]. В начале марта 2025 года Samsung получила от ASML первый сканер для производства чипов с нормами менее 2 нм. Это литографический сканер TwinScan EXE:5000, позволяющий работать с High-NA EUV. Опыт, полученный при использовании данного оборудования, пригодится Samsung при массовом производстве чипов по технологиям тоньше 2 нм[107]. В начале апреля 2025 года стало известно, что компания временно отложила разработку 1,4-нанометрового процесса, чтобы сосредоточиться на 2-нм и 1-нм направлениях[108]. Японская Rapidus надеется освоить 1,4-нм техпроцесс. Глава японского производителя пояснил, что до конца десятилетия ей предстоит приступить к освоению 1,4-нм технологии, иначе она безнадёжно отстанет от всего остального мира[109]. 1 нмСовместный центр исследований и разработок Samsung Electronics и ASML представит машины для литографии с высокой числовой апертурой не позднее 2027 года[110]. TSMC вскоре начнёт закладывать основы для техпроцесса 1 нм. Компания уже приступила к планированию строительства завода, способного выпускать продукцию по нормам 1 нм, в научном парке Цзяи — компания явно уверена, что продолжит развиваться в области полупроводников и сохранит доминирование на рынке производства чипов. Она направила властям города предложение о застройке участка площадью 100 га — он будет поделён 40/60 между заводами по производству упаковки и чипов по нормам 1 нм. TSMC, как сообщается, опередила всех других претендентов. Инвестиции компании в технологию 1 нм составляют более 1 трлн тайваньских долларов (32 млрд $). В декабре 2023 года TSMC представила дорожную карту, указывающую на намерение запустить производство чипов по нормам 1 нм к 2030 году. В сочетании с трёхмерной гетерогенной интеграцией она сможет выпускать процессоры с более чем 1 трлн транзисторов на чипе[111][112]. В начале февраля 2025 года TSMC начала подготовку к запуску на своей новой фабрике 1 нм производственные линии. Предприятие TSMC по выпуску 1-нм чипов расположится в городе Тайнань на юге острова Тайвань. Площадка получила обозначение Fab 25 и со временем приютит до шести предприятий, специализирующихся на выпуске чипов. Первые три завода (P1, P2 и P3) будут ориентированы на выпуск 1,4-нм чипов и появятся в первую очередь, позднее будут достроены ещё три (P4, P5 и P6), в которых со временем будет освоен выпуск 1-нм чипов. Массовый выпуск 12-дюймовых пластин на Fab 25 будет осуществляться на 12 линиях. Сроки запуска 1 нм линий поставлены на 2030 год. Если же TSMC ускорит освоение техпроцессов в этом диапазоне, то три первых предприятия на площадке Fab 25 сразу начнут выпуск 1-нм продукции, а три последующих будут специализироваться уже на 0,7-нм[113][114]. Компания Intel представила бизнес-единицу под названием Intel Foundry и новый техпроцесс Intel 14A — первый техпроцесс за пределами разрабатываемой сейчас группы. Также компания анонсировала ещё более тонкий техпроцесс — Intel 10A. Процессор Intel 10a будет первый CPU класса 1 нм. Компания собирается начать массовое производство продукции по нормам Intel 10A уже к концу 2027 года[115][116]. В начале апреля 2025 года компания Samsung сформировала специальную группу по созданию 1-нанометрового техпроцесса. Компания называет этот проект полупроводниковым "процессом мечты". Массовое производство чипов по этой технологии начнется не раньше 2029 года. Для реализации амбициозного плана Samsung потребуются более совершенные машины High-NA. Их цена — около $400 млн за штуку — вдвое выше текущих затрат TSMC на литографию. Компания, в отличие от TSMC, уже получила от ASML несколько таких машин[117]. <1 нмВ 2021 году IBM и Samsung совместно объявили о прорыве в проектировании полупроводников с использованием новой архитектуры вертикального транзистора (VTFET), способную резко увеличить производительность и энергоэффективность будущих процессоров, а также вывести их за пределы 1 нм. По сравнению с современными чипами FinFET потребление энергии чипами VTFET ниже на 85 %, а производительность — выше вдвое[118][119]. Бельгийский исследовательский центр ИМЕК сотрудничает с мировыми лидерами в сфере производства чипов, а потому его руководство может представлять путь развития всей полупроводниковой отрасли на несколько лет вперёд. По его мнению, к 2037 году производители чипов смогут освоить техпроцесс A2, а тремя годами позже удастся преодолеть барьер в 0,1 нм. Если исходить из принятых TSMC обозначений, техпроцесс A2 соответствует литографическим нормам 2 ангстрема (0,2 нм). Таким образом, в 2040 году полупроводниковая отрасль может преодолеть барьер в 1 ангстрем (0,1 нм), если предсказания главы Imec Люка ван ден Хова (Luc Van den hove) оправдаются. Свои заявления он сделал на технологическом форуме в Тайване, работу которого широко освещали местные СМИ[120]. В нанолистовой технологии Forksheet (FSFET), применение которой ожидается начиная с техпроцесса 1 нм, в одной конструкции совмещают транзисторы разной полярности, за счёт чего их становится возможным расположить почти вплотную, всего лишь через небольшой слой диэлектрика. Такие пары разнополярных транзисторов (КМОП-сборки, комплементарные пары) используются в чипах почти везде, и слипание их вместе на 20 % повышают общую плотность транзисторов. Переход на эту технологию должен обеспечить рост производительности на 10 % с сохранением потребления или сокращение потребления на 24 % без прироста производительности[121]. Начиная с техпроцесса 0,5 нм (5 ангстрем), комплементарные пары транзисторов предполагается располагать вертикально (CFET). Затем начиная с техпроцесса 0,2 нм (2 ангстрема) планируется уменьшение толщины каналов с целью уменьшения их длины за счет замены кремния двумерными материалами — атомарно-плоскими монослоями, такими как графен, сульфиды или селениды вольфрама или молибдена[122][123]. ПримечаниеВ мае 2025 года учёные из Пекинского университета представили транзистор, который может переопределить будущее микроэлектроники. Команда под руководством профессора Пенг Хайлина анонсировала кремниевый транзистор на основе двумерного материала — оксиселенида висмута (Bi2O2Se). Разработка использует архитектуру gate-all-around (GAAFET), где затвор полностью окружает канал, в отличие от частичного покрытия в традиционных FinFET-структурах. Это увеличивает площадь контакта, снижая утечку энергии и улучшая управление током. Новый транзистор демонстрирует на 40% более высокую скорость работы и на 10% меньшее энергопотребление по сравнению с современными 3-нанометровыми чипами Intel. По заявлению Пекинского университета, это «самый быстрый и эффективный транзистор из когда-либо созданных», который также превосходит процессоры TSMC и Samsung. Результаты тестов, проведённых в условиях, идентичных тем, что используются для ведущих коммерческих чипов, подтверждают эти показатели. Ключевым элементом стали новые материалы: Bi2O2Se в роли полупроводника и Bi2SeO5 в качестве диэлектрика затвора. Их низкая межфазная энергия минимизирует дефекты и рассеяние электронов. «Электроны движутся практически без сопротивления, как вода по гладкой трубе», — пояснил Пенг. Технология уже проверена с помощью расчётов теории функционала плотности (DFT) и физических испытаний на производственной платформе университета. Новая структура способна преодолеть ограничения миниатюризации кремниевых чипов, особенно при нормах ниже 3 нм. Это открывает перспективы для создания компактных и мощных процессоров, включая чипы для ноутбуков. Важно, что производство таких транзисторов возможно на существующей полупроводниковой инфраструктуре, что упростит их интеграцию в промышленность. Если технологию удастся масштабировать, то она может замедлить переход на альтернативные материалы, вроде графена, сохранив доминирование кремния в микроэлектронике[124]. См. также

Примечания

Литература

Ссылки

|

Portal di Ensiklopedia Dunia