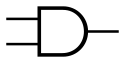

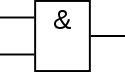

õĖÄķŚ©

õĖÄķŚ©’╝łĶŗ▒Ķ¬×’╝ÜAND gate’╝ēµś»µĢ░ÕŁŚķĆ╗ĶŠæõĖŁÕ«×ńÄ░ķĆ╗ĶŠæõĖÄńÜäķĆ╗ĶŠæķŚ©’╝īÕŖ¤ĶāĮĶ¦üÕÅ│õŠ¦ń£¤ÕĆ╝ĶĪ©ŃĆéõ╗ģÕĮōĶŠōÕģźÕØćõĖ║ķ½śķø╗ÕŻō’╝ł1’╝ēµŚČ’╝īĶŠōÕć║µēŹõĖ║ķ½śķø╗ÕŻō’╝ł1’╝ē’╝øĶŗźĶŠōÕģźõĖŁĶć│ÕżÜµ£ēõĖĆõĖ¬ķ½śķø╗ÕŻōµŚČ’╝īÕłÖĶŠōÕć║õĖ║õĮÄķø╗ÕŻōŃĆ鵏óÕÅźĶ»ØĶ»┤’╝īõĖÄķŚ©ńÜäÕŖ¤ĶāĮµś»ÕŠŚÕł░õĖżõĖ¬õ║īĶ┐øÕłČµĢ░ńÜäµ£ĆÕ░ÅÕĆ╝’╝īĶĆīµł¢ķŚ©ńÜäÕŖ¤ĶāĮµś»ÕŠŚÕł░õĖżõĖ¬õ║īĶ┐øÕłČµĢ░ńÜäµ£ĆÕż¦ÕĆ╝ŃĆé µ”éĶ┐░õĖŗÕłŚÕīģµŗ¼ķĆ╗ĶŠæķŚ©ńÜä3ń¦Źń¼”ÕÅĘ’╝ÜÕĮóńŖČńē╣ÕŠüÕ×ŗń¼”ÕÅĘ’╝łANSI/IEEE Std 91-1984’╝ēŃĆüIECń¤®ÕĮóÕøĮµĀć’╝łõĖŁÕøĮÕż¦ķÖå’╝ēń¼”ÕÅĘ’╝łIEC 60617-12’╝ēÕÆīõĖŹÕåŹõĮ┐ńö©ńÜäDINń¼”ÕÅĘ’╝łDIN 40700’╝ēŃĆéÕģČõ╗¢ńÜäķĆ╗ĶŠæķŚ©ń¼”ÕÅĘĶ¦üķĆ╗ĶŠæķŚ©ń¼”ÕÅĘĶĪ©ŃĆé

ĶŗźõĖÄķŚ©ńÜäÕģČõĖŁõĖĆõĖ¬ĶŠōÕģźÕÅ¢ÕÅŹÕłÖµłÉõĖ║ń”üķŚ©’╝łINHIBIT logic gate’╝īINHIBITOR’╝ēŃĆé Õ«×ńÄ░õĖÄķŚ©µś»Õ¤║µ£¼ńÜäķĆ╗ĶŠæķŚ©’╝īÕøĀµŁżÕż¦ÕżÜµĢ░ÕŹŖÕ»╝õĮōÕłČķĆĀÕĢåķāĮõ╝Üńö¤õ║¦Ķ┐Öń¦ŹķøåµłÉńöĄĶĘ»ŃĆéõŠŗÕ”é’╝īÕ£©TTLķøåµłÉńöĄĶĘ»7408ÕÆīCMOSķøåµłÉńöĄĶĘ»4081ÕØćńö▒ÕøøõĖ¬2ĶŠōÕģźõĖÄķŚ©µ×䵳ÉŃĆé

õĖÄķŚ©ķĆÜÕĖĖńö©nķĆÜķüō’╝łNMOS’╝ēµł¢pķĆÜķüō’╝łPMOS’╝ēńÜäMOSFETÕ«×ńÄ░ŃĆéµĢ░ÕŁŚĶŠōÕģźaõĖÄbÕ╝ĢĶĄĘĶŠōÕć║F’╝īĶ┐ÖÕÆīõĖÄķŚ©ńÜäÕŖ¤ĶāĮõĖĆĶć┤ŃĆé ÕżćķĆēµ¢╣µĪł Õ”éµ×£µ▓Īµ£ēńÄ░µłÉńÜäõĖÄķŚ©’╝īÕłÖÕÅ»ńö©õĖÄķØ×ķŚ©{x and y=(x nand y)nand (x nand y)}µł¢µł¢ķØ×ķŚ©{(x and y=(x nor x)nor(y nor y)}µØźÕ«×ńÄ░’╝īÕøĀõĖ║õĖÄķØ×ķŚ©ÕÆīµł¢ķØ×ķŚ©Ķó½Ķ«żõĖ║µś»ŌĆ£ķĆÜńö©ńÜäķĆ╗ĶŠæķŚ©ńöĄĶĘ»ŌĆØ[1]’╝īÕøĀõĖ║ķĆÜĶ┐ćĶ┐ÖõĖżń¦ŹķŚ©ńöĄĶĘ»ÕÅ»õ╗źÕ«×ńÄ░ÕģČõ╗¢µēƵ£ēķŚ©ńöĄĶĘ»ńÜäÕŖ¤ĶāĮŃĆéĶŗźńö©õĖÄķØ×ķŚ©Õ«×ńÄ░õĖÄķŚ©’╝īÕłÖÕ░åõĖĆõĖ¬õĖÄķØ×ķŚ©ńÜäõĖżõĖ¬ĶŠōÕģźń╗ōÕ£©õĖĆĶĄĘ’╝īńäČÕŠīÕ£©ÕģČĶŠōÕģźń½»µÄźÕģźõĖĆõĖ¬ÕÅīĶŠōÕģźńÜäõĖÄķØ×ķŚ©’╝øĶŗźńö©µł¢ķØ×ķŚ©Õ«×ńÄ░õĖÄķŚ©’╝īÕłÖÕ░åõĖżõĖ¬ĶŠōÕģźµÄźÕ£©õĖĆĶĄĘńÜ䵳¢ķØ×ķŚ©ÕłåÕł½õĮ£ÕÅ”Õż¢õĖĆõĖ¬µł¢ķØ×ķŚ©ńÜäõĖżõĖ¬ĶŠōÕģź’╝īńäČÕŠīÕ£©ÕŠīĶĆģńÜäĶŠōÕģźµÄźõĖĆõĖ¬ĶŠōÕģźµÄźÕ£©õĖĆĶĄĘńÜ䵳¢ķØ×ķŚ©ŃĆéÕ╝鵳¢ķŚ©õ╣¤ÕÅ»ńö©µØźÕ«×ńÄ░õĖÄķŚ©’╝īõĮåÕŠłÕ░æõĮ┐ńö©ŃĆé ÕÅéĶ¦üń╗┤Õ¤║Õģ▒õ║½ĶĄäµ║ÉõĖŖńÜäńøĖÕģ│ÕżÜÕ¬ÆõĮōĶĄäµ║É’╝ÜõĖÄķŚ© ÕÅéĶĆāµ¢ćńī«

Õż¢ķā©ķĆŻńĄÉ |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Portal di Ensiklopedia Dunia